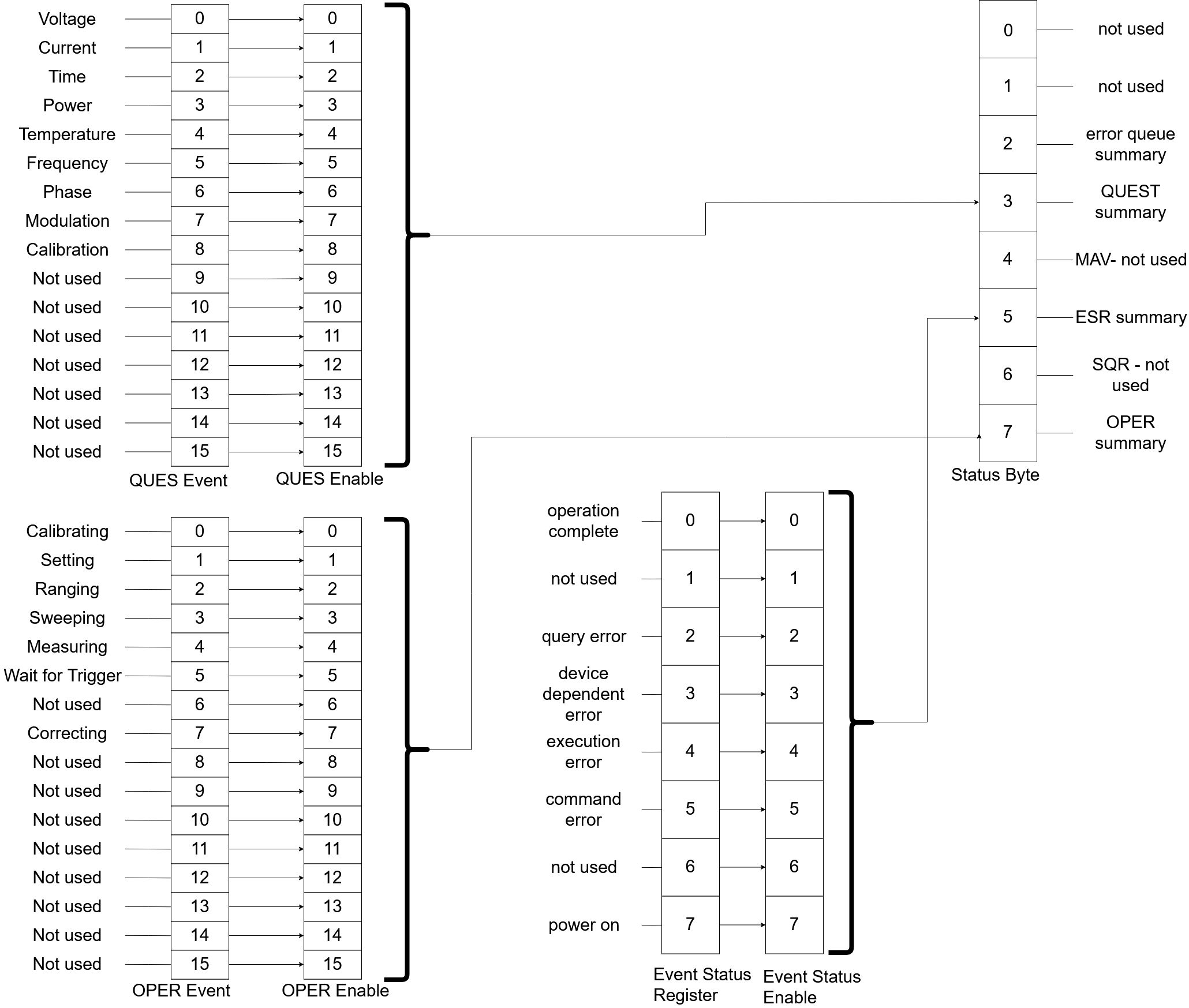

The status register system

Status registers are used for monitoring the state of the device. In these registers operation statusses, errors, events, and questionable data results are stored.

There are 4 main registers:

| Abbreviation | Full name | used for |

|---|---|---|

| STB | Status Byte Register | Contains summary of all underlying registers. |

| QUES | Questionable Status Register | Represents all measurement parameters whose quality is not 100% accurate (e.g. because of an overload). |

| OPER | Operation Status Register | Represents all ongoing operations and the current state of the device. |

| ESR | Standard Event Status Register | Contains all errors and events that happened either while parsing a message or while executing. |

Additional to the registers an Error and Event Queue stores all the enabled errors and events alongside with their info message.

The interaction of these registers is shown in the following picture:

Status Byte Register

The status byte register acts as the main summary register that combines all the underlying status registers.

| Bit value | code | description |

|---|---|---|

| Bit 0 - 1 | Available to designer |

not used |

| Bit 1 - 2 | Available to designer |

not used |

| Bit 2 - 4 | Error/Event Queue |

indicates that the error event queue is NOT empty |

| Bit 3 - 8 | Questionable Status Summary |

indicates that some devices values are questionable and thereforethe quality of the measurement is not guaranteed |

| Bit 4 - 16 | Message Available |

indicates that a message is available in the output queue. (Not used for the RAW Socket) |

| Bit 5 - 32 | Event Status Register Summary |

indicates that an event or an error occurred |

| Bit 6 - 64 | User Request |

Not used for the actual measurement device, because RAW socket does not support service requests. |

| Bit 7 - 128 | Operation Status Summary |

indicates that the device is currently performing some operations |

Standard Event Status Register

The Standard Event Status Register contains all bits for possible error types as well as operation complete and power on events. It can be read with *ESR?. The reading of the register clears its content. This register cannot be set, but is rather a representation of the devices status and therefore it can only be read. Between the ESR and the status byte register there is a event status enable register (ESE). The ESE register can be read and written. It selects which bits of the ESR register should be forwarded to the 5th bit of the STB register. The 5th bit of the STB is calculated as a logical OR of the enabled bits of the ESR register.

E.g.:

- When the ESE register is 255 (all bits are enabled), the 5th bit of the STB is set if at least one of the bits in the ESR is set.

- When the ESE register is 0 (all bits are disabled), the 5th bit of the STB is never set.

- When the ESE register is 1 (only bit 1 -

operation completeis enabled), the 5th bit of the STB is only set if the bit 1 of the ESR is set.

The individual values of the bits are:

| Bit value | code | description |

|---|---|---|

| Bit 0 - 1 | Operation complete |

Is set after an Operation Complete Command command, when all pending operations have finished. |

| Bit 1 - 2 | Request control |

Not used for the actual measurement device, because RAW socket does not support service requests. |

| Bit 2 - 4 | Query error |

Is set, when a query error occurs. |

| Bit 3 - 8 | Device dependent error |

Is set, when a device dependent error occurs. |

| Bit 4 - 16 | Execution error |

Is set, when an error occurs while executing a command. |

| Bit 5 - 32 | Command error |

Is set, when a given command is not valid. |

| Bit 6 - 64 | User Request |

Not used for the actual measurement device, because RAW socket does not support service requests. |

| Bit 7 - 128 | Power On |

Is set, when the device detects and off to on transition in its power supply. |

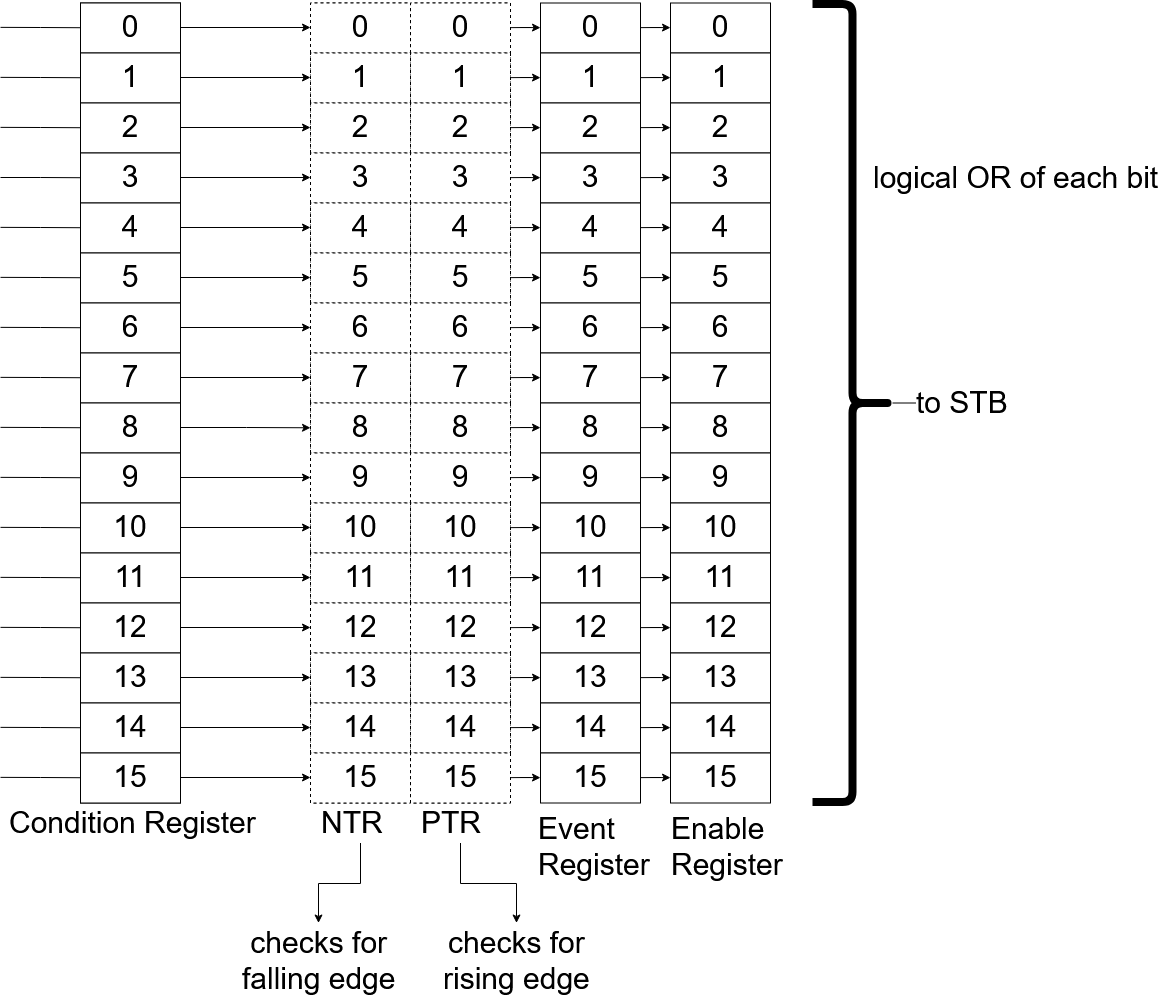

Event Based Status Register Groups

The Questionable and Operation Status Register are both event based status register groups, which adds more functionality to their usage.

Basically each event based register group contains 5 individual register:

| Name | Settable | Gettable | Usage |

|---|---|---|---|

| Condition | NO |

YES |

automatically set/reset by the device if an action occurs. |

| Positive transition filter | YES |

YES |

Selects which positive transitions should be noticed. |

| Negative transition filter | YES |

YES |

Selects which negative transitions should be noticed. |

| Event | NO |

YES |

All events that passed through the transition filters are stored here. |

| Enable | YES |

YES |

Selects which bits of the Event Register should be considered for the summary that is stored in the STB. |

Positive Transition

A positive transition is defined as the change of a bit from 0 to 1. If the positiv transition filter is set and the according bit in the Condition Register changes from 0 to 1, the according bit in the Event Register is set.

The positive transition filter is useful when you want to get notified if an action has started (e.g. the measuring bit changes from 0 to 1 when a measurement starts).

By default, all positive transitions are enabled.

Negative Transition

A negative transition is defined as the change of a bit from 1 to 0. If the negative transition filter is set and the according bit in the Condition Register changes from 1 to 0, the according bit in the Event Register is set.

The negative transition filter is useful when you want to get notified if an action is finished (e.g. the measuring bit changes from 1 to 0 when the measurement stops).

By default, all negative transitions are disabled.

Usage

So the summarize, if you want that the summary bit in the STB register is set, when a register value changes, you have to set two values:

- Either the bit in the positive or the negative transition filter, depending on which transition you are interested in.

- The bit in the

EnableRegister, so that the selected bit is forwared to the STB.

Questionable Status Register

The Questionable Status Register is an Event Based Register as explained above. The values of the individual bits are listed below.

| Bit value | code | description |

|---|---|---|

| Bit 0 - 1 | VOLTage |

The quality of the voltage measurement can not be guaranteed. |

| Bit 1 - 2 | CURRent |

The quality of the current measurement can not be guaranteed. |

| Bit 2 - 4 | TIME |

The quality of the time measurement can not be guaranteed. |

| Bit 3 - 8 | POWer |

The quality of the power measurement can not be guaranteed. |

| Bit 4 - 16 | TEMPerature |

The quality of the temperature measurement can not be guaranteed. |

| Bit 5 - 32 | FREQuency |

The quality of the frequency measurement can not be guaranteed. |

| Bit 6 - 64 | PHASe |

The quality of the phase measurement can not be guaranteed. |

| Bit 7 - 128 | MODulation |

The quality of the modulation can not be guaranteed. |

| Bit 8 - 256 | CALIbration |

The quality of the calibration can not be guaranteed. |

| Bit 9 - 512 | Not used |

This bit is not used. |

| Bit 10 - 1024 | Not used |

This bit is not used. |

| Bit 11 - 2048 | Not used |

This bit is not used. |

| Bit 12 - 4096 | Not used |

This bit is not used. |

| Bit 13 - 8192 | INSTrument Summary |

A summary of the instruments register. |

| Bit 14 - 16384 | Command Warning |

Not used by now. |

| Bit 15 - 32768 | Not used |

The usage of the most significant bit is not allowed since some controllers may have difficulty reading a 16 bit unsigned integer. |

The available commands to access the Questionable Status Register are:

Operation Status Register

The Operation Status Register is an Event Based Register as explained above. The values of the individual bits are listed below.

| Bit value | code | description |

|---|---|---|

| Bit 0 - 1 | CALIbrating |

The device is calibrating. |

| Bit 1 - 2 | SETTing |

The device is setting. |

| Bit 2 - 4 | RANGing |

The device is ranging. |

| Bit 3 - 8 | SWEeping |

The device is performing a sweep. |

| Bit 4 - 16 | MEASuring |

The device is performing a measurement. |

| Bit 5 - 32 | Waiting for TRIGger Summary |

The device is waiting for a trigger signal. |

| Bit 6 - 64 | Waiting for ARM Summary |

The device is waiting for ARM. |

| Bit 7 - 128 | CORRecting |

The device is performing some corrections. |

| Bit 8 - 256 | Not used |

This bit is not used. |

| Bit 9 - 512 | Not used |

This bit is not used. |

| Bit 10 - 1024 | Not used |

This bit is not used. |

| Bit 11 - 2048 | Not used |

This bit is not used. |

| Bit 12 - 4096 | Not used |

This bit is not used. |

| Bit 13 - 8192 | INSTrument Summary |

A summary of the instruments register. |

| Bit 14 - 16384 | PROGram Running |

A program is running. |

| Bit 15 - 32768 | Not used |

This bit is not used. |

The available commands to access the Operation Status Register are:

Error/ Event Queue

The Error and Event Queue stores all errors and events that occurred. An entry consist of an error number, an error title and optionally an additional information to the error. The numbers titles and meanings can be found under Error List of all posible errors.

The queue implements the FIFO (first in first out) principle, always the first error that occurred is read first. If an entry is read, it is removed from the queue.

If the queue is already empty, a no error string, which has the same structure as an error (number and title - can be found at @errors) is returned.

Only the error and event types that are enabled by the ESE (Event Status Enable) register, are added to the queue. The second bit of the STB indicates if there are entries left in the queue, waiting to be read.

The queue is cleared when calling *CLS.

Commands: